## - 5.5 Electrical interface

• Please provide the instrument power budget analysis in each operation mode and state what margin level is used.

## MEPS A + MEPS B 36 ADCs

3 channels single gain and 3 channels dual gain for each MEPS Detector Package Preamps = 6\*2 + 6\*2 = 24 Shapers = 9\*2 + 9\*2 = 36

MEPS detector package(2per sensor, 2 sensors per unit, 2units) 9 channels per package, 18 channels per sensor, 36 channels per unit.

| QTY | DESCRIPTION                                                                                                          | POWER / mW | POWER TOTAL / | misc Infos comments                                                  | Board                                    |

|-----|----------------------------------------------------------------------------------------------------------------------|------------|---------------|----------------------------------------------------------------------|------------------------------------------|

| 12  | Preamps (1 BF862 FET @ 5V, 1 AD8005 +-5V Iq=0,4mA)                                                                   | 14.00      | 168           | MEPS A preamps                                                       | MEPS A Filter &<br>Preamp                |

| 12  | LDO dissipation loss for BF862, power supply from +6V analog                                                         | 4.00       | 48            | it's just one LDO for FET                                            | MEPS A Filter &<br>Preamp                |

| 1   | 3x (LDO PREAMP POS + LDO PREAMP NEG + JFET) 4 OPS 4*2.2ma*6V=52.8mW (LDO quiescence power)                           | 52.80      | 5.3           | LDO quiescence power, 10P is unused                                  | MEPS A Filter &<br>Preamp                |

|     | LDO dissipation loss for AD8005 power supply from +-<br>6V analog (0.4mA*(2*6V-2*5V))=0.8mW                          | 0.80       |               | just four LDOs for +V-PA and -V-PA                                   | MEPS A Filter &<br>Preamp                |

|     | 0. and 203 (0. max (2. 5. 2. 5.77) 0. com.                                                                           | 0.00       |               | Jaco 2002 2009 201 11 111 111 111 111                                | MEPS B PREAMP +                          |

| 12  | Preamps (1 BF862 FET @ 5V, 1 AD8005 +-5V Iq=0,4mA) LDO dissipation loss for BF862, power supply from                 | 14.00      | 168           | MEPS B preamps                                                       | FILTER MEPS B PREAMP +                   |

| 12  | 3x (LDO PREAMP POS + LDO PREAMP NEG + JFET) 4 OPS                                                                    | 4.00       | 48            | it's just one LDO for FET                                            | FILTER MEPS B PREAMP +                   |

|     | 13x (LDO PREAMP POS + LDO QUIESCENCE POWER)  LDO dissipation loss for AD8005 power supply from +-                    | 52.80      | 53            | LDO quiescence power, 10P is unused                                  | FILTER MEPS B PREAMP +                   |

|     | 6V analog (0.4mA*(2*6V-2*5V))=0.8mW                                                                                  | 0.80       | 10            | just four LDOs for +V-PA and -V-PA                                   | FILTER                                   |

| 36  | Shaper (1 AD8005 +-5V Iq-0,4mA)                                                                                      | 4.00       | 144           | HET + EPT shaper                                                     | ANALOG FPGA<br>SHAPER ADC<br>ANALOG FPGA |

| 38  | 12bit 8Channel ADC ADC128S102QML (1.5mA @ 3.3V)                                                                      | 4.95       | 188           | 30x ADC shaper 2x ADC housekeeping                                   | SHAPER ADC<br>ANALOG FPGA                |

| 1   | RTAX2000S radiation hardened FPGA - ACTEL misc amplifiers, misc electronic, temperature                              | 270.00     | 270           | ADC interface, level trigger                                         | SHAPER ADC<br>ANALOG FPGA                |

| 1   | sensors, LDOs                                                                                                        | 150.00     | 150           | temperature, divider misc electronic                                 |                                          |

| 1   | multiple reference voltages                                                                                          | 35.00      |               | with reference chip and resistor<br>divider for multiple voltages    | DIGITAL                                  |

|     | LDO dissipation loss for AD8005 power supply from +-6V analog (0.4mA*(2*6V-2*5V))=0.8mW                              | 0.80       |               | just four LDOs for +V-SH, -V-SH, +V-PA and -V-PA                     |                                          |

|     | 2x (LDO SHAPER POS + LDO SHAPER NEG) 2 OPS<br>2*2.2mA*6V=26.4mW (LDO quiescence power)                               | 26.40      |               | LDO quiescence power for shapers                                     | DIGITAL                                  |

|     | RTAX2000S radiation hardened FPGA — ACTEL RAM 16Mbit (2M x 8), SRAM, with continuously write                         | 440.00     |               | processing softcore EDAC UART<br>data and softcore program SRAM EDAC | DIGITAL                                  |

|     | cycles<br>oscillator (20mA € 3.3V)                                                                                   | 90.00      |               | UART ADC interface<br>Main clock for FPGA                            | DIGITAL<br>DIGITAL                       |

|     | UT54LVDM055LV 1 out TX, 1 in RX, 1 in 1HZ NOM & RED (27.5mA @ 3.3V)                                                  | 90.75      | 182           | lTx, lRx, lHz-clock NOM & RED                                        | DIGITAL                                  |

|     | 80% switching regulator 5059RH for FPGA core voltage                                                                 |            |               |                                                                      |                                          |

| 1   | 1.5V                                                                                                                 | 177.50     | 178           | switching regulator V-Digital                                        | POWER                                    |

|     | 80% switching regulator 5059RH for IO voltage 3.3V<br>80% switching regulator 5059RH for analog ADC                  | 70.63      |               | switching regulator V-Digital                                        | POWER                                    |

|     | voltage 3.3V<br>PWM switching frequency synchronisation crystal                                                      | 47.03      |               | switching regulator V-ADC                                            | POWER                                    |

|     | oscillator and CD4024<br>2x (LDO ANALOG POS + LDO ANALOG NEG) 2 OPs                                                  | 132.00     |               | synchronisation with LVPS<br>LDO quiescence power for analog         | POWER                                    |

|     | 2*2.2mA*6.7V=29.48mW (LDO quiescence power) LDO dissipation loss for analog power supply from +- 6.7V analog to +-6V | 131.08     |               | voltage<br>LDO dissipation loss for analog LDOs                      | DIGITAL                                  |

|     | POWER                                                                                                                | 131.00     |               | POWER total all obove                                                |                                          |

|     | LOW VOLTAGE POWER SUPPLY (electrical Efficiency:                                                                     |            |               |                                                                      | POWER                                    |

|     | 70%, VIN: 28V, VOUT: 4.9V, 2x6.8V, 21V, 12V, 12V)                                                                    |            |               | power loss LVPS<br>TOTAL (no heater)                                 | POWER                                    |

|     |                                                                                                                      |            |               | + Margin 20%                                                         |                                          |

estimation for activity of 100% at 25°C

Figure 1: MEPS instrument power consumption estimation

o Please provide your instrument local ground scheme.

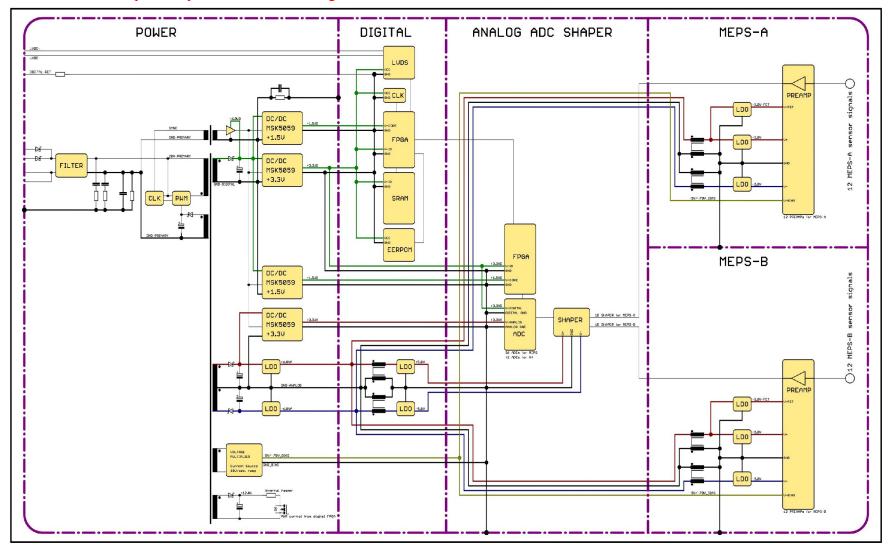

Figure 3: MEPS instrument ground schematic

- o Please provide some information about the DC-DC converter you plan to use in your instrument, e.g. what secondaries are required? what efficiency you expect it to achieve at normal load? is this DC-DC transformer isolated(it should be)? Is it an off-the-shelf product or customized circuit?

- The voltage converter for the low voltage power supply (LVPS) is a flyback converter topology build with the Pulse width modulator(PWM).

- The clock frequency of the PWM generator is externally synced to 125kHz switching frequency(250kHz external sync). This frequency will be generated by a crystal oscillator with 2MHz. With this frequency divider the frequency of 1MHz for the secondary switching regulators (MSK5059) will be provided also. A common mode choke will be used as transformer to provide these switchers with external sync frequency.

- The PWM and the secondary switchers has adjusted frequency of around 75% of the desired and will be trimmed to the desired. So, when external sync to the wished fails, these regulators will run anyway.

- The flyback converter is regulated to a secondary output on the primary side, which will provide the PWM itself and the crystal oscillator with its frequency divider. So, no optocoupler is needed in this configuration.

- The outputs of the positive and negative analog voltages of the flyback converter has a down streamed LDO to minimize noise and provide a stable voltage for the further boards.

- The analog voltage for the ADCs(3.3V) will be provided by a switching regulator also, with an additional passive filter.

- The digital voltages will be provided by switching regulators (Vcore for FPGA 1.5V, VDigital IO 3.3V).

- There are two 12V output secondary voltages. One is the operating voltage of the PWM and clock along with the frequency divider and the second secondary 12V is for the internal heaters if necessary.