# Solar Orbiter HET/EPT Digital FPGA

# Stephan I. Böttcher

# ${\rm SVN~Revision~8147} \\ {\rm Date~2020\text{-}12\text{-}03~21\text{:}53\text{:}06~+0100~(Do,~03~Dez~2020)}$

Document code: SO-EPD-KIE-DA-0001 Issue 1 Rev 0.3

# Contents

| 1 | Intr | roduction                        | 6          |

|---|------|----------------------------------|------------|

| 2 | Mo   | de of Operation                  | 6          |

|   | 2.1  | Data Acquisition                 | 7          |

|   | 2.2  | Data Checkout                    | 7          |

|   | 2.3  | Slow Control                     | 7          |

|   | 2.4  |                                  | 8          |

|   |      | 2.4.1 Serial Commands via LVDS   | 8          |

|   |      |                                  | 9          |

|   | 2.5  | Master Control Message           | 9          |

|   | 2.6  |                                  | 10         |

|   |      |                                  | 10         |

|   |      |                                  | 11         |

|   |      |                                  | 11         |

|   |      | 2.6.4 Analog Trigger Event Data  | 12         |

|   |      |                                  | 12         |

| 3 | Tele | emetry packets                   | L <b>2</b> |

|   | 3.1  | Serial Packet Format             | 13         |

|   | 3.2  |                                  | 13         |

|   |      | 3.2.1 Status and Error Registers | 14         |

|   |      | 3.2.2 Address Registers          |            |

|   |      |                                  | 15         |

|   |      | 9                                |            |

|   |     | 3.2.4   | UART Status                                           |

|---|-----|---------|-------------------------------------------------------|

|   |     | 3.2.5   | Heater Registers                                      |

|   | 3.3 | Histog  | gram Data                                             |

|   |     | 3.3.1   | Data Product Scheduler                                |

|   |     | 3.3.2   | Data Compression                                      |

|   |     | 3.3.3   | Unencoded Data                                        |

|   | 3.4 | Memo    | ry Readout                                            |

|   |     | 3.4.1   | External SRAM                                         |

|   |     | 3.4.2   | EEPROM Readout                                        |

|   |     | 3.4.3   | Configuration Table Readout                           |

|   |     | 3.4.4   | Counter Readout                                       |

|   |     | 3.4.5   | Memory Index Registers                                |

|   | 3.5 | Fronte  | end Readout                                           |

|   |     | 3.5.1   | Analog Readout Items                                  |

|   |     | 3.5.2   | Analog Housekeeping                                   |

|   |     | 3.5.3   | Temperature Capture                                   |

|   |     | 3.5.4   | Peeking                                               |

|   |     | 3.5.5   | Single Channel Trigger Counters                       |

|   | 3.6 | L2 Str  | reaming                                               |

|   |     | 3.6.1   | Samples Readout                                       |

|   | 3.7 | Monit   | oring Parameters                                      |

|   |     | 3.7.1   | Register readout                                      |

|   |     | 3.7.2   | Histogram Data                                        |

|   |     | 3.7.3   | Counter Memory Readout                                |

|   |     | 3.7.4   | HET-EPT Analog Frontend Readout 30                    |

|   | ъ.  |         |                                                       |

| 4 |     |         | uisition 31                                           |

|   | 4.1 |         | Height Data Packets                                   |

|   |     | 4.1.1   | Event Packet Reception                                |

|   |     | 4.1.2   | L3 Event Class                                        |

|   | 4.0 | 4.1.3   | Trigger and Prescale Counters                         |

|   | 4.2 |         | Buffer                                                |

|   |     | 4.2.1   | Feeding the L3 trigger processor                      |

|   |     | 4.2.2   | PHA storage                                           |

|   |     | 4.2.3   | Test Data Injection                                   |

|   | 4.9 | 4.2.4   | Event Data Formats                                    |

|   | 4.3 | L3 trig |                                                       |

|   |     | 4.3.1   | HIST Instruction                                      |

|   | 1 1 | 4.3.2   | PHA Instruction                                       |

|   | 4.4 |         | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|   | 4.5 | Sampl   | le Mode                                               |

|   | 4.6 | Timestamp Clock                            | 10       |

|---|-----|--------------------------------------------|----------|

| 5 | Ope | erational Heater 4                         | .1       |

|   | 5.1 | Heater Modes of Operation                  | 11       |

| 6 | Coı | int Rate Series Compression 4              | 2        |

|   | 6.1 | Histogram Windows                          | 12       |

|   | 6.2 | Counter Cadence                            | 12       |

|   | 6.3 | Compression Unit                           | 13       |

|   |     | 6.3.1 Encoder                              | 13       |

|   |     | 6.3.2 Basic Encoder Operations             | 14       |

|   |     | 6.3.3 Cadence Sequence without Compression | 15       |

|   |     | 6.3.4 Compression Sequence                 | 15       |

|   |     | 6.3.5 Compression Sequence with Summing    | 17       |

|   |     |                                            | 17       |

|   | 6.4 |                                            | 17       |

|   |     | 6.4.1 Encoding in Full Poisson Resolution  | 18       |

|   |     |                                            | 19       |

|   |     |                                            | 19       |

|   |     |                                            | 19       |

| 7 | EEI | PROM 5                                     | 0        |

|   | 7.1 | EEPROM Page Write                          | 50       |

|   |     | O                                          | 50       |

|   |     |                                            | 51       |

|   |     |                                            | 51       |

| 8 | Inn | uts and Outputs 5                          | 1        |

| O | _   | Power                                      |          |

|   | 8.2 | The clocks                                 |          |

|   | 0.2 | 8.2.1 TODO                                 |          |

|   | 8.3 | ICU Asynchronous Serial Link               |          |

|   | 0.0 | v                                          | 53       |

|   |     | ·                                          | 54       |

|   |     |                                            | 54       |

|   | 8.4 |                                            | 55       |

|   | 0.4 | ·                                          | 55       |

|   | 8.5 |                                            | )<br>56  |

|   | 0.0 |                                            |          |

|   |     | 0 0                                        | 56<br>56 |

|   |     | Ų Ų                                        | 90<br>58 |

|   |     |                                            |          |

|    | 8.6   | PWM output                                                     | 58 |

|----|-------|----------------------------------------------------------------|----|

|    | 8.7   | Device Pinouts                                                 | 58 |

| 9  | Tmn   | lementation Details                                            | 58 |

| 9  | 9.1   |                                                                | 58 |

|    | 9.1   | External Memory Access                                         |    |

|    |       | 9.1.1 Memory Port to Arbitration Unit Interface                | 59 |

|    |       | 9.1.2 Memory Driver Interface                                  | 59 |

|    |       | 9.1.3 Memory drivers                                           | 59 |

|    |       | 9.1.4 Memory Port                                              | 60 |

|    |       | 9.1.5 Memory Port Priorities                                   | 61 |

|    |       | 9.1.6 Memory EDAC                                              | 61 |

|    | 9.2   | UART                                                           | 62 |

|    |       | 9.2.1 Baud Rate Generator                                      | 62 |

|    |       | 9.2.2 Abort Sequence                                           | 63 |

|    |       | 9.2.3 PPS Receiver                                             | 63 |

|    | 9.3   | Serializer/Deserializer                                        | 64 |

|    | ~1    |                                                                |    |

| 10 | Cha   | ingelog                                                        | 64 |

|    |       |                                                                |    |

| L  | ist ( | of Tables                                                      |    |

|    |       | 01 165165                                                      |    |

|    | 1     | Digital Board Counters, frontend L2 triggers                   | 22 |

|    | 2     | Digital Board Counters, SEU Errors                             | 23 |

|    | 3     | Digital Board Counters, communication                          | 23 |

|    | 4     | Digital Board, Trigger Counters                                | 24 |

|    | 5     | Digital Board, UART                                            | 24 |

|    | 6     | Analog Housekeeping Readings                                   | 27 |

|    | 7     | Parameters to extract from the register readout packet. Offset |    |

|    |       | is in bytes, length is in bits                                 | 29 |

|    | 8     | Frontend parameters                                            | 31 |

|    | 9     | Event Pulse Height Packet Format                               | 32 |

|    | 10    | L3 Data Set Format                                             | 33 |

|    | 11    | L3 instruction opcodes                                         | 38 |

|    | 12    | Sample Packet Format                                           | 40 |

|    |       |                                                                | 43 |

|    | 13    | Cadence Modulus Table                                          |    |

|    | 14    | Encoding Format without Drop                                   | 48 |

|    | 15    | Encoding Format with Drop=3                                    | 49 |

|    | 16    | Input and Output Ports                                         | 52 |

|    | 17    | Engineering to Flight Mapping of Memory Ports                  | 57 |

# List of Figures

| 1 | Proposed LVDS Termination Circuit | 54 |

|---|-----------------------------------|----|

| 2 | LV-PECL Termination Schematic     | 55 |

# 1 Introduction

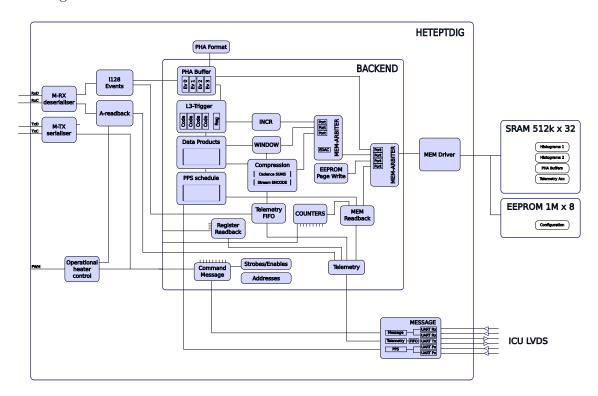

The HET/EPT sensor employs two FPGAs, one each on the analog and the digital boards. The FPGA on the analog board will control the ADCs, perform digital filtering, L1 and L2 trigger processing, and housekeeping acquisition. The digital board FPGA is described in this document.

# 2 Mode of Operation

The operations of the FPGA are grouped in three threads of execution:

- 1. data acquisition,

- 2. data checkout, and

- 3. slow control.

All functions are controlled via command messages and a *Pulse Per Second* (PPS) signal. Both command messages and PPS signals can be received from the ICU and generated autonomously in the FPGA.

During nominal operation, the PPS is received once per second from the ICU and the necessary command messages are generated inside the FPGA synchronized to the PPS. No command messages from the ICU are required during nominal operation.

Command messages for configuration and slow control need to be send by the ICU via LVDS serial communication.

### 2.1 Data Acquisition

Data acquisition involves

- 1. reception of event data packets from the analog FPGA,

- 2. buffering (up to four packets),

- 3. L3 trigger processing,

- 4. histogram counting, and

- 5. PHA data storage.

Histograms and PHA data are stored in the external SRAM. The storage areas are double buffered, one buffer for acquisition and one being checked out for telemetry.

Once configured and enabled, the data acquisition operates completely autonomously.

#### 2.2 Data Checkout

In parallel to the data acquisition, the checkout proceeds from data acquired previously. The execution of the checkout is controlled by a command table in the PPS scheduler. The scheduled tasks include

- starting and stopping data acquisition between acquisition periods,

- switch buffers between acquisitions,

- perform analog housekeeping acquisitions and telemetry,

- send counters and other status housekeeping,

- send PHA data buffers,

- kick the operational heater,

- reconfigure the frontend, to clear out SEU,

- calculate and send histogram data telemetry.

#### 2.3 Slow Control

Once configured and operational, there shall be no or very little commanding of the sensor from the ICU. Tasks that may arise during operation include

• changing trigger parameters,

- initiate diagnostic telemetry, or

- writing new data into the EEPROM.

Writing into configuration memory to tune trigger parameters should be safe at any time as long as the changes do not change the trigger algorithm and leave the trigger operational between all writes. The analog frontend configuration is not normally changed directly, but stored in the PPS scheduler and updated once per second between acquisitions.

Diagnostic telemetry must not be initiated during telemetry checkout, else the data streams collide and garbage is emitted. The PPS schedule shall include spots that are reserved for synchronous actions, like EEPROM page write or diagnostic telemetry. The command to execute the action will be written into reserved slots in PPS schedule table. A further entry in the table will automatically clear the command message from the table after is was emitted, so it will be executed only once.

Writing EEPROM pages is safe as long as the memory port occupation does not interfere. EEPROM access is rather slow and blocks the external memory bus. The execution of the EEPROM page write shall be synchronized to the PPS schedule.

### 2.4 Command Messages

A command message includes three items:

- an address (14 bit),

- a size tag (2 bits), and

- a data word (64 bits).

The address identifies the recipient of the message. The size tag indicates how many bits shall be interpreted from the data word:

- 0: zero bits,

- 1: 16 bits,

- 2: 32 bits, or

- 3: 64 bits.

Most recipients ignore the size tag and just accept as much of the data word as they need. Bits beyond the indicated size are expected to be zero.

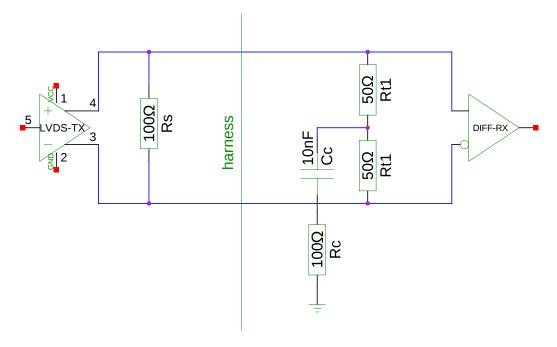

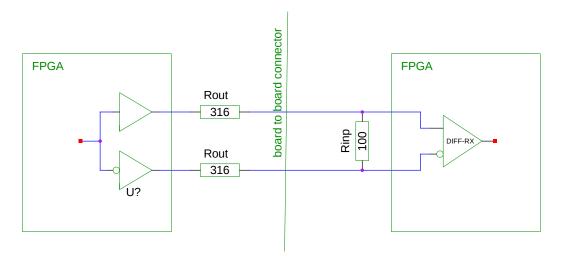

#### 2.4.1 Serial Commands via LVDS

Messages are received from the ICU via LVDS signaling through a UART operating at 115 200 baud. The serial message format is specific to the Kiel

sensor units:

| 0x 3c3d                                            |

|----------------------------------------------------|

| $\langle sz \rangle$ $\langle address \rangle$     |

|                                                    |

|                                                    |

|                                                    |

| $\langle data \rangle (\langle sz \rangle \geq 1)$ |

| < <i>crc&gt;</i>                                   |

The CRC is computed according to the following parameters as defined in http://www.ross.net/crc/download/crc\_v3.txt

$$\begin{array}{ll} \text{WIDTH} &= 16 \\ \text{POLY} &= 0 \text{x} \, 1021 \\ \text{INIT} &= 0 \text{x} \, \text{ffff} \\ \text{REFOUT} &= 0 \\ \text{REFIN} &= 0 \\ \text{XOROUT} &= 0 \text{x} \, 0000 \end{array}$$

Only as many data words are transmitted as indicated by the  $\langle sz \rangle$  tag. The received message data is padded to the left with zeros to fill 64 bits. Word and byte ordering is big endian.

#### 2.4.2 PPS scheduled messages

The PPS scheduler emits messages that are indistinguishable from serially received messages, i.e., the recipients cannot tell where they came from. There is only one difference: the PPS scheduler can emit data words with nonzero bits beyond the indicated size. That should not matter, because those recipients that do look at the size tag ignore the data beyond the indicated size.

# 2.5 Master Control Message

A message to address  $0x\,0000$  issues strobes<sub>64</sub>. These are simple command pulses to trigger some action or effect. Most of the strobes set or clear enables<sub>8</sub> or confs<sub>16</sub> bits, so these act more like master control registers.

$strobes_{64}[23:16]$  set the corresponding bits in  $enables_8$ .  $strobes_{64}[31:24]$  clear those bits. A bit that is both to be set and cleared will be toggled.

Similarly,  $strobes_{64}[47:32]$  set, and  $strobes_{64}[63:48]$  clear bits in  $confs_{16}$ . Most bits in  $confs_{16}$  are unused.

#### Command message:

| 3  | C           | 0x 0000      |                      |                     |

|----|-------------|--------------|----------------------|---------------------|

|    | clr c       | $onfs_{16}$  | set co               | $\mathfrak{s}_{16}$ |

| c] | Lr enables8 | set enables8 | actions <sub>8</sub> | resets <sub>8</sub> |

### 2.6 Link to the Analog Board

Communication between the digital board FPGA and the analog board FPGA goes over synchronous serial links, with a data and a clock signal for each direction, with LVDS signaling. The clock frequency is 48 MHz. The clock towards the analog board is used as the master clock of the analog FPGA.

The serial links employ 20-bit frames to transfer 16-bit words over two channels. Two bits provide a synchronization edge, one bit selects the channel, one bit can be used for line balancing, but here it is just toggled for each frame.

#### Synchronous serieal link frames:

| 1 | 0 | i | c |     |     |     |   |   |   | < da | ta  | > |   |   |   |   |     |

|---|---|---|---|-----|-----|-----|---|---|---|------|-----|---|---|---|---|---|-----|

|   |   |   |   | 4 1 | - 1 | - 1 | 1 | 1 | 1 | - 1  | 1 1 |   | ı | 1 | 1 | 1 | - 1 |

Bit c is zero for control channel data and one for stream channel data. When no data is to be sent, the link transfers a control message of zero. When the i bit is set, all the remaining bits of the frame are inverted. A stream of control messages zero will include exactly one falling edge per frame, regardless of the i-bit. Link synchronization can always be immediately recovered when the link is idle.

These links provide four channels, two in each direction, which operate all independently.

Control Digital to Analog: Enables and strobes,

Stream Digital to Analog: command messages,

Control Analog to Digital: status and configuration readback, and

Stream Analog to Digital: data acquisition.

#### 2.6.1 Command Messages to the Analog Board

Command messages can be sent to the analog board FPGA via the stream channel. The messages complies to the IRENA command format, with 14

address bits and none or 16 data bits.

| Ρ | Ana   | lo | g Board           | Command Messag            | <u>z</u> ∈ |  |  |  |  |  |  |

|---|-------|----|-------------------|---------------------------|------------|--|--|--|--|--|--|

|   | 1 p   | 0  | $0_{1}0_{1}0_{1}$ | $\langle address \rangle$ |            |  |  |  |  |  |  |

| Г | .7.4. |    |                   |                           |            |  |  |  |  |  |  |

The  $\langle data \rangle$  frame is only present when the p bit is set. The analog board responds to a subset of the address range with 10 valid address bits, and four most significant bits zero.

There are two ways to generate messages to the analog board, either with the command message described here, or with an analog readback command described in section 3.5.

#### Command message:

| $\langle sz \rangle 0 1 0 0 \langle address \rangle$ |                    |

|------------------------------------------------------|--------------------|

| <data 3=""></data>                                   | <data 2=""></data> |

| <data 1=""></data>                                   | <data 0=""></data> |

If the command has  $\langle sz \rangle = 0$ , a message without data is sent. Otherwise the command data is send in multiple messages to consecutive addresses on the analog board. The word ordering is little endian.

#### 2.6.2 Analog Board Responses

When the analog board returns data in response to a command messages, the data is sent through the control channel, using two frames per 16-bit data word. Each returned word is prefixed with a fixed header. This allows to distinguish data words with content zero from the idle link.

The analog board returns data only when it receives an analog readback command described in section 3.5.

#### 2.6.3 Analog Frontend Control

The control channel to the analog board is used to send states and strobes. The channel can support up to 15 state bits and up to 15 strobes.

When a strobe needs to be sent, a control word is sent with the most significant data bit zero, and the strobe set in the corresponding bit position.

```

a strobes<sub>16</sub>[1]=strobes<sub>64</sub>[14]: random, trigger,

a strobes<sub>16</sub>[3]=strobes<sub>64</sub>[3]: timestamp clock reset,

a strobes<sub>16</sub>[13]=strobes<sub>64</sub>[4]: readback FIFO reset,

```

```

a strobes<sub>16</sub>[14]=strobes<sub>64</sub>[5]: data FIFO reset.

```

Every few microseconds, the digital board will send a control message with the most significant data bit set. The remaining bits are enable bits which will be latched by the analog board to control is operations.

```

a states<sub>16</sub>[0]=enables<sub>8</sub>[5]: analog master enable, a states<sub>16</sub>[1]=confs<sub>16</sub>[1]: samples mode enable, a states<sub>16</sub>[3]=enables<sub>8</sub>[4]: timestamp clock enable, a states<sub>16</sub>[13]=confs<sub>16</sub>[6]: readback disable, a states<sub>16</sub>[14]: event buffer full.

```

#### 2.6.4 Analog Trigger Event Data

The stream channel from the analog board is used to transfer trigger event data packets. Two types of packets are supported, pulse height event packets, and sample packets. When sample packets are enabled, the analog board will not send pulse height event packets.

#### 2.6.5 High Speed Calibration Mode

In nonflight operation during calibration campains it is very desirable to acquire data at high rate from the analog board. For this purpose it is possible to send the data stream from the analog board directly to the redundant LVDS link.

This mode is enabled by setting bit  $confs_{16}[0]$ . Reception of commands in the redundant receiver is not impacted by activating high speed mode.

The data and clock from the analog board are time multiplexed on the single redundant line. A microframe of four bits at 96 Mbps consists of the sequence 0, 1, A, and B, with two data bits A and B. The GSE samples the stream at 384 MHz, identifies the rising edges, and extracts data and clock, which are then decoded by an instance of the same module as present in the digital board FPGA.

# 3 Telemetry packets

Telemetry emitted by the FPGA is tagged with an APID. Eight bits xx of the APID can be arbitrarily configured for each packet emitted. These bits shall steer the processing of the packet in the ICU. The upper eight bits distinguish the included data types:

0x 01xx: Register readout.

0x 03xx: Histogram data.

0x 05xx: Memory readout.

0x 08xx: Frontend readout.

0x 57EA: L2 streaming. (TBC)

The last packet type shall not ever be issued when the sensor is integrated. These packets are issued in L2 streaming mode, where all frontend data packets are sent directly to the serial line. This function will be used for sensor calibration. This mode is someimes referred to as *Slow Speed Streaming*, to distinguish it from the *High Speed Streaming* of the analog board bitstream via the redundant channel.

#### 3.1 Serial Packet Format

Telemetry packets are sent to the ICU in the STF packet format defined for EPD. The first two bytes of the STF packet payload is the APID.

| 0x beba                |  |  |  |  |  |  |  |  |  |  |  |

|------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 0x cafe                |  |  |  |  |  |  |  |  |  |  |  |

| 0, 0, 0 $n+4$          |  |  |  |  |  |  |  |  |  |  |  |

| $\langle apid \rangle$ |  |  |  |  |  |  |  |  |  |  |  |

| <data></data>          |  |  |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |  |  |

| < <i>crc&gt;</i>       |  |  |  |  |  |  |  |  |  |  |  |

# 3.2 Register Readout

A register readout is initiated with a corresponding command message. The message address is the same as the issued APID, i.e.,  $0 \times 01xx$ . The message shall have 16 bits of data, which select from a set from 16 items to be sent in the resulting telemetry packet. Each item results in 64 bits of data.

| Con | Command message: |   |   |     |   |   |   |   |   |   |     |   |   |   |

|-----|------------------|---|---|-----|---|---|---|---|---|---|-----|---|---|---|

| 1   |                  | ı | 0 | x0: | 1 |   |   |   | ı |   | xx  |   | ı | ı |

|     | ı                | ı | ı | ı   | ı | ı | ı | ı | ı | ı | _3_ | 2 | 1 | 0 |

The items selected by the given bit number are

0: status and error registers,

1: address registers,

- 2: modulus timer registers,

- 3: scratch register,

- 4: Nominal Uart and PPS status.

- 5: Redandant UART and PPS status.

- 6: heater registers,

All other items are reserved, they return zeros.

#### 3.2.1 Status and Error Registers

confs<sub>16</sub> and enables<sub>8</sub> are control bits that are set and cleared with a master control message. version<sub>8</sub> is a constant identifier of the FPGA and the version of the code. errors<sub>8</sub> are bits that are set when something happened.

#### Register 0 Readout:

| trigger           | $class_{16}$         | con:                 | $fs_{16}$           |

|-------------------|----------------------|----------------------|---------------------|

| misc <sub>8</sub> | enables <sub>8</sub> | version <sub>8</sub> | errors <sub>8</sub> |

The  $misc_8$  bits are zero, except for bit  $misc_8[0]$ , which is the state of the EEPROM BUSY signal.

The error bits are cleared by  $strobes_{64}[7]$ .

errors<sub>8</sub>[7:6]: 0 (unused)

errors<sub>8</sub>[5]: lost synchronization to analog board,

errors<sub>8</sub>[4]: ATBRK received,

errors<sub>8</sub>[3]: single-bit error in the external SRAM,

errors<sub>8</sub>[2]: multi-bit error in the external SRAM,

errors<sub>8</sub>[1]: single-bit error in FPGA RAM,

$errors_8[0]$ : multi-bit error in FPGA RAM.

#### 3.2.2 Address Registers

These are address pointers for various memory related operations.

#### Register 1 Readout:

| 0                      | dum                   | $\operatorname{pp}\operatorname{page}_{12}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|------------------------|-----------------------|---------------------------------------------|-------------------------------------------------------|

| miscpage <sub>19</sub> | enc page <sub>6</sub> | pha base7                                   | pha page <sub>12</sub>                                |

#### 3.2.3 Modulus Timer Registers

All of the FPGA's notion of time.

#### Register 2 Readout:

| i fini <sub>3</sub> | $ $ init $_3$ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ | $\begin{smallmatrix} \mod count_{12} \\ \vdash $ |

|---------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                   | usec                                                  | $ond_{24}$                                                                                                                                                              |

The i bit set when the PPS scheduler is not active.

The modulus scheduler counts  $\mu$ seconds divided down from the FPGA clock. At each  $\mu$ second it issues a tick. Messages from the PPS scheduler are issued in phase with the  $\mu$ second tick, messages from the ICU are delayed to fall in the middle of the tick period, to not collide with PPS scheduler messages. The EEPROM page write delays are derived from the  $\mu$ second tick.

A PPS or  $strobes_{64}[2]$  resets the  $\mu$ seconds counter. The counter is 24-bits long, so we can support PPS intervals up to 16 seconds.

The modulus scheduler counts seconds (as defined by the PPS interval) in a cycles of length 3600, i.e., one hour. The  $mod count_{12}$  reflects the current second within that cycles. The cycle is reset by a  $strobes_{64}[1]$ . The cycle is factored into seven data acquisition cadence counters

$$3600 = 5 \times 2 \times 3 \times 2 \times 5 \times 2 \times 6$$

Three moduli in the range 0...7 mark significant times in the cycle.  $mod_3$  marks the beginning of a data acquisition cadence periods. All cadence levels at or below  $mod_3$  are beginning in the current second.

fini<sub>3</sub> marks the end of the cadence periods. All cadence levels at or below fini<sub>3</sub> end in the current second. This modulus tells how many data products are generated in the current second.

init<sub>3</sub> is a rather complicated modulus used to initialize encoding sequences. All encoded data product with acquisition cadence equal fini<sub>3</sub> and encoding cadence at or below init<sub>3</sub> will initialize an new compression sequence in this second.

fini<sub>3</sub> and init<sub>3</sub> are part of the science data packet headers. The parser obviously needs to know these moduli to decode the data bitstream.

#### 3.2.4 UART Status

The status of the UART and PPS receiver.

#### Register 4/5 Readout:

| uart status9    | 0         | ppsflags7            |         | $\mathtt{length}_{16}$ | 1 1 1 |

|-----------------|-----------|----------------------|---------|------------------------|-------|

| $length_{16}$ 0 | 1 1 1 1 1 | period <sub>26</sub> | 1 1 1 1 | 1 1 1 1                | 1 1 1 |

```

uart status<sub>9</sub>[8]: AT-break active.

uart status 9[7]: RX break active.

uart status_9[6]: RX busy.

uart status<sub>9</sub>[5]: RX active.

uart status_9[4]: RX frame error.

uart status<sub>9</sub>[3]: RX line status.

uart status<sub>9</sub>[2]: PPS line status.

uart status_9[1]: TX empty.

uart status_9[0]: TX break (not used, alway zero).

ppsflags<sub>7</sub>[6]: PPS is good.

ppsflags<sub>7</sub>[5]: PPS is selected.

pps flags<sub>7</sub>[4]: PPS is too seldom, i.e., two PPS received on the other line.

pps flags<sub>7</sub>[3]: PPS is too long, longer than 500 \,\mu s.

pps flags<sub>7</sub>[2]: PPS is too short, shorter than 1 \mu s.

pps flags<sub>7</sub>[1]: PPS is too fast, more than 5 ms too early.

ppsflags<sub>7</sub>[0]: PPS is too slow, more than 5 ms too late.

length<sub>16</sub>: PPS length, in units of 24 MHz clocks.

period<sub>26</sub>: PPS period error, in units of 24 MHz clocks.

```

#### 3.2.5 Heater Registers

The temperature, resulting duty cycle of the operational heater, and remaining heater time in PWM cycles. See section 5.

### Register 6 Readout:

| 0 | · · · · · · · · · · · · · · · · · · · | duration <sub>24</sub> |

|---|---------------------------------------|------------------------|

| 0 | dutycycle <sub>8</sub>                | ) temp $_{12}$         |

## 3.3 Histogram Data

A command message to the *Data Product Scheduler* (DPS) will initiate the assembly of a histogram data packet. These are the main data products of

the sensor.

Command message:

| 3 |   | ı | ۱, | )x() | 3 | ı |        |     |    | $x_{\mid}x$      | : | <br>ı |   |       |   |       |   |   |   |     |                    |          |

|---|---|---|----|------|---|---|--------|-----|----|------------------|---|-------|---|-------|---|-------|---|---|---|-----|--------------------|----------|

|   | ı |   |    |      |   | L |        | L   |    |                  |   | ı     | ı | ı     |   | <br>1 | ı | ı | ı |     | $flg_2$            | $tmod_3$ |

|   | 1 | _ | ,  |      |   | ı | <br>ad | ldŗ | eș | s <sub>1,1</sub> | 1 | <br>, |   | <br>1 | , | 1     | 1 |   |   | cou | $\mathtt{nt}_{12}$ |          |

This command instructs the DPS to execute  $count_{12}$  items starting at address<sub>11</sub> from the data products table. If the current modulus is at least  $tmod_3$ , the resulting data will be sent in a telemetry packet.

The payload of the data packet is a stream of items with varying bit sizes, starting with an 8-bit header telling the cadence modulus, followed by optionally compressed histogram counter sums. The last byte is filled with unspecified bits. The format of the header is

The flg<sub>2</sub>-bits from the command message are included in the 8 bit packet header. They carry no semantics within the sensor unit and can be used to multiplex up to four data product streams into one CCSDS telemetry packet stream.

The packet is assembled in a special telemetry FIFO, to establish the packet size before transmission is started. This FIFO can assemble packets of up to  $2\,\mathrm{kBytes}$ .

#### 3.3.1 Data Product Scheduler

A table with 2048 entries configures individual histogram window sums. A window sum is calculated as the sum of histogram counters from a 2-dimensional region in the external memory.

Data Product Table Item:

|               |         | ystrid                          | 916 <sub>1 1 1 1 1</sub> |     | 1 1 2 | size <sub>8</sub> |    | xsize <sub>8</sub> |

|---------------|---------|---------------------------------|--------------------------|-----|-------|-------------------|----|--------------------|

| ${\sf res}_3$ | $enc_3$ | $\operatorname{\mathtt{sum}}_3$ | $c$ $t$ $a$ $comp_2$     | 1 1 |       | addr              | 18 |                    |

Three bits have these meanings:

- c: Clear each histogram memory word after reading.

- t: Send the result to the telemetry.

- a: Add the result of the previous data product.

The c-bit is used to clear the histogram memory for the next acquisition. The DPS can be started with a message-id  $0 \times 02xx$ , instead of  $0 \times 03xx$ , which will prevent the assembly of a data packet, e.g., for clearing a memory region.

The a-bit can be used to build more complex data products. An item with the a-bit shall follow an item without the t-bit. The first sum is not sent for compression, but included in the following data item.

The memory window is defined by  $\mathtt{addr}_{18}$ ,  $\mathtt{xsize}_8$ ,  $\mathtt{ysize}_8$ , and  $\mathtt{ystride}_{16}$ . The sum starts at  $\mathtt{addr}_{18}$ . The address is incremented  $\mathtt{xsize}_8$  times by one. Then it is incremented by  $\mathtt{ystride}_{16}$  and the run through the x is repeated. The  $\mathtt{ystride}_{16}$  increment happens  $\mathtt{ysize}_8$  times. The total number of memory locations being added is

$$(x \operatorname{size}_8 + 1) \times (y \operatorname{size}_8 + 1)$$

The MSB of the memory address is the complement of enables<sub>8</sub>[3], i.e., the hist page bit, selecting the part of memory not currently used for data acquisition.

#### 3.3.2 Data Compression

A data item that has the t-bit set is sent to the compression engine. The compression is controlled by  $sum_3$ ,  $enc_3$  and  $res_3$ .

The DPS will execute every second. Most data products shall be produced at a longer cadence. The sum<sub>3</sub> modulus tells the compressor for how long to sum the data before transmission. The data packet will be generated every second, but include only data items that have run their summing period. The modulus values are given in Table 13 on page 43.

The res<sub>3</sub> modulus shall be the same as the sum<sub>3</sub> modulus. If res<sub>3</sub> has a lower value than sum<sub>3</sub>, a sparse count rate is produced. The data is generated at the cadence specified in sum<sub>3</sub>, but the counter is reset at the cadence given in res<sub>3</sub>. Counts before the last reset are lost.

If res<sub>3</sub> has a larger value than sum<sub>3</sub>, the data sent will accumulate over multiple data items. This does not work with compression.

The enc<sub>3</sub> modulus tells the compressor for which stretches of time the lossy running difference compression shall be applied to the stream of counts. If enc<sub>3</sub> is not larger than sum<sub>3</sub>, the data will be send unencoded according to the format specified in comp<sub>2</sub>. Otherwise they are subject to further compression. The compression cycle is reset at the cadence given by enc<sub>3</sub>.

The compressor maintains a data record for each data product in main memory. Each record occupies four words. The base address is configured in encpage<sub>6</sub>, i.e., bits [18:13] of the memory address.

If a telemetry packet includes only data products that require summing, i.e., all  $sum_3 > 0$ , the data packets between the sums would include only the 8-bit header. The DPS shall be started with  $tmod_3$  equal to the smallest  $sum_3$ , to suppress these empty telemetry packets in between.

#### 3.3.3 Unencoded Data

Most science data will be encoded with variable bit sizes. The format of unencoded data is defined with two bits comp<sub>2</sub>, selecting one of four representations for the counters. The unencoded data is unsigned.

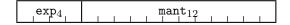

comp<sub>2</sub>=00: 16 bit unsigned floating point, 4-bit exponent.

$comp_2=01$ : 8 bit representing  $8 \cdot (\log_2(c) + 1)$ .

$comp_2=10$ : 24 bit unsigned integer.

comp<sub>2</sub>=11: encoded uncompressed counter.

The format of an unsigned 16-bit float is

The represented counter value is

$$\begin{split} C &= \mathtt{mant}_{12} & \text{for} \quad \mathtt{exp}_4 = 0, \\ C &= (\mathtt{mant}_{12} + 2^{12}) \cdot 2^{\mathtt{exp}_4 - 1} & \text{for} \quad \mathtt{exp}_4 > 0. \end{split}$$

The floating point or  $\log_2$  representations do not need to be converted to plain integers for comparisson to some threshold. The  $\log_2$  representation can be used in trigger or monitoring logic for ratio cuts.

# 3.4 Memory Readout

The memory readout engine can read words from various sources:

- external SRAM.

- external EEPROM.

- configuration tables in the FPGA

- PPS schedule table,

- data products table,

- L3 code memory,

- counters.

Readout is initiated with

#### Command message:

| 3 | 0x05                  |                      |

|---|-----------------------|----------------------|

|   | 1 1 1 1 1 1           | count                |

|   | $\dots$ count $_{11}$ | ${\tt address}_{24}$ |

The read data will be packed into a telemetry packet. Using message address  $0 \times 04xx$  will also perform the reads of the memory, but not transmit a packet. This can be used to perform EDAC scrubbing on configuration memories.

Which memory is read and how the final memory addresses are calculated is encoded in address<sub>24</sub>. The number of words read is count<sub>11</sub>. The word size depends on the kind of memory or is encoded in address<sub>24</sub> as well.

The telemetry packet payload is prefixed with 32 bits

#### Memory readout header:

| counts | $address_{2A}$ |

|--------|----------------|

|        |                |

Three most significant bits of  $count_{11}$  are omitted. The address<sub>24</sub> is the calculated read address of the first data word. This may be different from the address<sub>24</sub> given in the command message.

### 3.4.1 External SRAM

The external SRAM is read in words of 32 bits. No EDAC decoding is performed. The most significant bits of address<sub>24</sub> encode how the address shall be calculated:

0x8aaaaa: direct addressing,0x9aaaaa: histogram page,

OxAaaaaa: PHA page,

OxBaaaaa: misc page<sub>18:0</sub> indexed.

Direct addressing leaves the given address unchanged.

Histogram page access selects the half of the SRAM which is not currently being used for data acquisition, unless address<sub>24</sub>[18] is set, to access the active half.

For PHA page readout, three bit ranges of the memory address are replaced, based on the content of the phabase<sub>18:12</sub> and phapage<sub>11:0</sub> registers. phabase<sub>18:12</sub> points to the memory where PHA data is being stored by data acquisition. Readout address bit 18 is the complement of phabase[18]. Address bits [17:12] are replaced by the corresponding bits from phabase. The

lowest 12 bits are the sum of the address given in the command message and the phapage register.

The miscpage<sub>18:0</sub> register can be used for dribble readout of large memory regions. The same readout command is issued repeatedly from the PPS schedule, followed by an appropriate increment of the miscpage register. For PHA data readout the phapage register can be used in this fashion.

#### 3.4.2 EEPROM Readout

Readout of the EEPROM yields bytes, i.e., 8-bit words. Two modes are supported:

Ox Caaaaa: direct addressing,

Ox Faaaaa: misc page<sub>18:0</sub> indexed.

#### 3.4.3 Configuration Table Readout

The configuration tables are stored in 72-bit wide memory blocks inside the FPGA. Eight bits are used for EDAC redundancy, leaving 64-bits of information. Readout yields error corrected 64-bit words. Dribble readout is available via the dumppage11:0 register:

0x0C2aaa: direct addressing,

0x2C2aaa: dumppage<sub>11:0</sub> indexed.

The address ranges are

0x 0C2400-0x 0C25FF: L3 code.

0x 0C2600-0x 0C26FF: PPS schedule table.

0x 0C2800-0x 0C2FFF: data products table.

The word size is encoded in  $address_{24}[19:18]$  of the command message (0x 0c). If a smaller word size is specified, the words will be only partially transmitted. Don't do that.

#### 3.4.4 Counter Readout

The FPGA keeps a set of 128 counters in a memory block of width 36 bit. After EDAC correction the counters are 29 bits wide. dump page 11:0 indexing is available:

0x0800aa: direct addressing,

0x2800aa: dumppage<sub>11:0</sub> indexed.

The word size is encoded in  $address_{24}[19:18]$ . For the counter readout, three word sizes are implemented:

$0 \times 0800 aa$ : 32-bit unsigned integers.

0x 0400*aa*: 16-bit unsigned floating point, 12-bit mantissa, 0x 0000*aa*: 8-bit unsigned floating point, 3-bit mantissa.

Tables 1 to 5 list the counters provided by the HET-EPT digital board. Unused counters up to index 127 are present, but nothing increments them.

Only one counter can increment per clock cycle. An event to be counted will be latched until it gets access to the counter memory. When further events for the same counter occur before it could be submitted, the additional events will be lost.

Table 1: Digital Board Counters, frontend L2 triggers

| Index | Description                                     |

|-------|-------------------------------------------------|

| 0     | $\times 1$ triggers lost on the analog board.   |

| 1     | $\times 2$ triggers lost on the analog board.   |

| 2     | $\times 4$ triggers lost on the analog board.   |

| 3     | $\times 8$ triggers lost on the analog board.   |

| 4     | $\times 16$ triggers lost on the analog board.  |

| 5     | $\times 32$ triggers lost on the analog board.  |

| 6     | $\times 64$ triggers lost on the analog board.  |

| 7     | $\times 128$ triggers lost on the analog board. |

| 8     | L2 #0 triggers.                                 |

| 9     | L2 #1 triggers.                                 |

| 10    | L2 #2 triggers.                                 |

| 11    | L2 #3 triggers.                                 |

| 12    | L2 #4 triggers.                                 |

| 13    | L2 #5 triggers.                                 |

| 14    | L2 #6 triggers.                                 |

| 15    | L2 #7 triggers.                                 |

#### 3.4.5 Memory Index Registers

The memory index registers are manipulated by command messages. The values are read via register readout telemetry item 1.

histbase<sub>[18]</sub>=enables<sub>8</sub>[3]: This bit is used as address bit [18] for histogram data acquisition.

phabase<sub>18:12</sub>: Base address for PHA data storage.

Table 2: Digital Board Counters, SEU Errors

# Index Description

- 16 Counter memory uncorrectable SEU errors.

- 17 Telemetry FIFO uncorrectable SEU errors.

- 18 L3 register uncorrectable SEU errors.

- 19 Data product schedule uncorrectable SEU errors.

- 20 L3 trigger code uncorrectable SEU errors.

- 21 PPS schedule uncorrectable SEU errors.

- 22 (unused) reserved for frontend SEU errors.

- 23 SRAM uncorrectable SEU errors.

- 24 Counter memory single bit SEU errors.

- 25 Telemetry fifo single bit seu errors.

- 26 L3 register single bit SEU errors.

- 27 Data product schedule single bit SEU errors.

- 28 L3 trigger code single bit SEU errors.

- 29 PPS schedule single bit SEU errors.

- 30 (unused) reserved for frontend SEU errors.

- 31 SRAM single bit SEU errors.

Table 3: Digital Board Counters, communication

#### Index Description

- 32 PPS accepted.

- 33 PPS received via message.

- 34 PPS received via 1 Hz clock from ICU.

- 35 Data product packets.

- 36 Memory readout packets.

- 37 Register readout packets.

- 38 Frontend readout packets.

- 39 Packet collisions.

- 40 messages received from ICU.

- 41 messages executed from PPS schedule.

- 42 EEPROM bytes written.

- 43 EEPROM bytes read or written.

- 44 ATBRK received, errors<sub>8</sub>[4].

- 45 Lost analog board sync., errors<sub>8</sub>[0].

- 46 Unused.

- 47 Unused.

Table 4: Digital Board, Trigger Counters

| Index | Description                             |

|-------|-----------------------------------------|

| 48    | Lost events received from the frontend. |

| 49    | Data products encoded.                  |

| 50    | L3 trigger started.                     |

| 51    | PHA records stored/counted.             |

| 52    | Histogram windows computed.             |

| 53    | Histogram bin increments.               |

| 54    | Triggers received for class 0.          |

| 55    | Triggers received for class 1.          |

| 56    | Triggers received for class 2.          |

| 57    | Triggers received for class 3.          |

| 58    | TFIFO put while pushing.                |

| 59    | TFIFO init while sending.               |

| 60    | Window sum valid.                       |

| 61    | Floating point result valid.            |

| 62    | $\log_2(c)$ result valid.               |

| 63    | Compression result valid.               |

Table 5: Digital Board, UART

| Index | Description                                |

|-------|--------------------------------------------|

| 64    | Valid bytes received.                      |

| 65    | Invalid bytes received (STOP bit missing). |

| 66    | Messages received.                         |

| 67    | Message header format errors.              |

| 68    | Message timeouts.                          |

| 69    | CRC errors.                                |

| 70    | FIFO uncorrectable SEU errors.             |

| 71    | FIFO single bit SEU errors.                |

| 72    | Streaming mode: packet lost.               |

| 73    | Streaming mode: packet init.               |

| 74    | Streaming mode: packet submit.             |

| 75    | Streaming mode: packet put.                |

| 76    | Unused.                                    |

| 77    | Unused.                                    |

| 78    | Unused.                                    |

| 79    | Unused.                                    |

|       |                                            |

phapage<sub>11:0</sub>: Index register for PHA readout.

miscpage<sub>18:0</sub>: Index register for external memory dribble readout.

dump page<sub>11:0</sub>: Index register for internal memory dribble readout.

encbase<sub>18:13</sub>: Base address for the data compression memory.

And there is a scratch<sub>64</sub> register, which has no function at all, but shall be used as a versioning tool to inject into the telemetry, to help the parsers on the ground to figure out what configuration was used. The scratch<sub>64</sub> register is returned as readout item 3.

To manipulate the index registers the command message addresses are

```

0x 0004: pha base_{18:12}, pha page_{11:0} = \text{data}_{18:0}.

0x 0005: pha page_{11:0} = \text{data}_{11:0}.

0x 0006: pha base_{18:12} += \text{data}_{18:12}, pha page_{11:0} += \text{data}_{11:0}.

0x 0007: enc base_{18:13} = \text{data}_{18:13}.

0x 0008: misc page_{18:0} = \text{data}_{18:0}.

0x 0009: misc page_{18:0} increment.

0x 0000A: dump page_{11:0} = \text{data}_{11:0}.

0x 000B: dump page_{18:0} increment.

0x 000F: scratch_{64} = \text{data}_{64}.

```

hist base<sub>[18]</sub> is set or cleared with strobes from a master control message. The MSB of phabase<sub>18:12</sub>[18] can be toggled with strobes[11].

The miscpage<sub>18:0</sub> and dumppage<sub>18:0</sub> increment commands allow for quite a bit of flexibility to control the memory regions covered. The message data provides an increment amount, two masks, and a constant.

|                                            | $\mathtt{miscpage}_{18:0}$ | $\mathtt{dump}\mathtt{page}_{18:0}$ |

|--------------------------------------------|----------------------------|-------------------------------------|

| $<\!\!increment\ value\!\!>$               | $\mathtt{data}_{18:0}$     | $\mathtt{data}_{11:0}$              |

| <pre><increment mask=""></increment></pre> | $\mathtt{data}_{50:32}$    | $\mathtt{data}_{27:16}$             |

| $<\!\!keep\ mask\!\!>$                     | $\mathtt{data}_{50:32}$    | $\mathtt{data}_{43:32}$             |

| $<\!\!constant\!\!>$                       |                            | $\mathtt{data}_{59:48}$             |

The index register will be incremented by the *<increment value>*. All bit positions not set in the *<increment mask>* will be cleared from the sum. All bit positions set in the *<keep mask>* will be keep from the old value of the index register. Finally, all bits set in *<constant>* will be set in the index register.

Let's see how much of this is useful.

#### 3.5 Frontend Readout

A message to address 0x1ff on the analog board will initiate the return of an analog readback packet to the digital board. This data stream will normally be ignored by the digital board. A special analog readback command message can be used as an alternative way to issue such a readback message to the analog board

#### Command message:

| 2 | 0x.08     |             |                        |

|---|-----------|-------------|------------------------|

|   | 1 1 1 1 1 | tempoffset8 | ${\sf itemsmask}_{15}$ |

This command will save the telemetry tag xx and enable the transmission of the next analog readback packet wrapped into a telemetry packet with APID 0x 08xx.

The analog readback packet includes the items mask<sub>15</sub> as first data word. The digital board FPGA will use the returned mask to calculate the size of the packet. So, unfortunately, the engine that forwards the analog readback needs to have hardwired knowledge of the size of the items that may be returned.

#### 3.5.1 Analog Readout Items

The bits in the items mask<sub>15</sub> select the items that shall be returned. The items are variable sized blocks of 16-bit words.

- 0: Filter configuration, 8 words.

- 1: Trigger configuration, 92 words.

- 2: Timestamp clock, 2 words.

- 3: HK ADC readout, packed, 12 words.

- 4: HK ADC readout, unpacked, 16 words.

- 5: Raw sample peek, 30 words.

- 6: Pulse height peek, 30 words.

- 7: Pulse phase peek, 30 words.

- 8: Single channel trigger counter read, 30 words.

- 9: Single channel trigger counter read and clear, 30 words.

- 10: Single channel trigger counter clear only, 0 words.

Bits [14:11] are unused/reserved. The items are send starting with the highest selected bit.

#### 3.5.2 Analog Housekeeping

Sixteen ADC readings with 12-bit resolution are returned either packed, or unpacked one reading per words with the channel number prefixed.

Table 6: Analog Housekeeping Readings

HET preamp temperature

- 1 500 EPT preamp temperature 2 401 HET VREF,  $+2.5 \,\mathrm{V}$ 3 501 EPT sensor temperature 4 402 HET sensor temperature 1 5 502 EPT VFET/2, +5 V 6 403 HET VFET/2, +5 V 7 503 EPT VANA/2, +6 V 8 404 HET sensor temperature 2 9 EPT VREF,  $+2.5 \,\mathrm{V}$ 504 405 Shaper VCC/2, +5V10 11 505 Bias Current

- 12 406 Power board t

- 12 406 Power board temperature

- 13 506 Bias Voltage

400

- 14 407 Analog board temperature

- 15 507 Digital board temperature

#### 3.5.3 Temperature Capture

To control the operational heater, it may be necessary to know the temperature of the sensor unit. Among the items that can be returned from the analog board are readings of voltages and temperature sensors. When the tempoffset<sub>8</sub> field in the command message is non-zero, it will be used as a word offset into the returned analog readback packet. Twelve least significant bits from the indicated word will be copied to the temp<sub>12</sub> register. The tempoffset<sub>8</sub> shall point to a word from an unpacked HK ADC readout. Some packed HK ADC readout channels may also work if they are properly aligned.

To capture a temperature from an analog readout packet without issuing a telemetry packet, the command message can be issued with address  $0 \times 09xx$  instead of  $0 \times 08xx$ .

#### 3.5.4 Peeking

The digital filter continuously issues pulse height reconstruction parameters and raw ADC samples for each data acquisition channel. Peek readout cap-

tures a set of these values. Raw sample peek returns a set of ADC samples, to diagnose problems with the analog signal baselines. Pulse height/phase peeks may be useful to estimate noise amplitudes.

The digital filter needs to be enabled via enables<sub>8</sub>[5] for any peek to yield the expected data.

#### 3.5.5 Single Channel Trigger Counters

Each signal channel has a counter that increments when its L1 trigger threshold is exceeded. The counters can optionally be cleared after reading, or even be cleared without reading. The counters values are provided in 16-bit unsigned floating point representation with 12-bit mantissa.

### 3.6 L2 Streaming

When the data acquisition is enabled on the analog board, a trigger event packet is sent for every valid L2 trigger. Normally, this data is sent to the L3 trigger processor and, on request from L3, saved into PHA storage.

For calibration of the sensor it will be necessary to get direct access to the event packets. The bit confs<sub>16</sub>[2] enables L2 streaming mode, all event packets received from the analog board will be wrapped into a telemetry packet. L2 streaming uses the telemetry FIFO.

When the fifo is full, the packets trying to get in will be dropped.

#### 3.6.1 Samples Readout

The analog board FPGA can be set to samples mode. Instead of trigger event packets, L2 triggers will issue a configurable stream of sample packets, including consecutive sets of raw ADC readings. This is like a 30 channel digital oscilloscope, and can be used to diagnose the pulse shapers.

Samples mode is enabled by setting bit  $confs_{16}[1]$ . If streaming mode is enabled as well, the packets will be sent to telemetry.

Sample packets will be forwarded to the L3 trigger, and can be saved in PHA buffers. This may lead to scenarios to use sample mode in flight for troubleshooting, with readout through PHA storage.

### 3.7 Monitoring Parameters

The Sensor unit will send several packets to the ICU for purposes other than being forwarded to the spacecraft and to ground, i.e,

• monitoring sensor status and health,

- data to be sent in s20 packets,

- trigger burst mode, and

- detect high particle rate conditions.

These functions need information from the sensor unit. The ICU will extract values from sensor packets and store them in its global parameters storage. Parameter extraction is governed by a table in the ICU configuration that specifies for each extractable parameter:

- a parameter-ID,

- the sensor-ID,

- the packet-APID,

- byte offset into the packet,

- length in bytes of the value to extract, big endian,

- a mask (32 bits) to clear selected bits from the value.

A parameter is identified by a 16-bit parameter-ID.

This section lists possible/proposed parameters to extract from sensor packets, and how they may become useful.

#### 3.7.1 Register readout

Sensor status is extracted via register readout, as described in section 3.2. Table 7 assumes that the first seven registers are read, i.e., the register mask is 0x007F. With a different mask the offsets will change. The STEP sensor may define more registers that may require monitoring, these may be added to the table in the future.

Table 7: Parameters to extract from the register readout packet. Offset is in bytes, length is in bits.

| Name        | offset | length | description                         |

|-------------|--------|--------|-------------------------------------|

| status      | 2      | 64     | variius status and error bits       |

| time        | 22     | 12     | cadence counter, second of the hour |

| duty cycle  | 56     | 8      | OP heater duty cycle                |

| temperature | 57     | 12     | OP heater temperature reference     |

#### 3.7.2 Histogram Data

A packet with data derived from the acquired histograms will be formatted for the ICU, i.e., without variable length encoding. Most of these will be

8 bits values representing the eight times the logarithm of base two of the counter value. This format is suitable to be directly put into s20 packets as requested by RPW.

The format is also suitable for relative trigger cuts, because differences in parameter values represent ratios of counter values.

A second useful format available is 16 bits unsigned floating point representations of counter values. These can be directly compared to thresholds, since the representation interpreted as an unsigned integer is monotonous with the represented counter value.

For absolute difference trigger cuts, the counters can be represented as plain integers in 24 bits.

The packet from an HET-EPT sensor shall include

- ten  $\log_2$  values from EPT as requested by RPW, covering four energy ranges for electrons and one energy range for ions, from two directions, at a time resolution of 1 s.

- the same ten values at time resolution 10 s,

- further data from HET and EPT as required.

The data items must be sorted by time resolution. Longer cadence data needs to be appended to shorter cadence data, so that each data item is always at the same byte offset in the packet.

The ICU will reserve a set of parameter-IDs for trigger parameters that can be configured during the mission to extract the required data items for monitoring and trigger purposes. The parameters to be sent in \$20 will be alloated with fixed IDs. Triggers can use any parameters available, including the \$20 parameters.

#### 3.7.3 Counter Memory Readout

The digital board counters may include items which are useful for monitoring or trigger purposes. Event or trigger counters can be used to identify high rate environments. SEU error counters may be used to monitor sensor health. Message counters can flag unusual activity, i.e., for a flag in a status word that indicates a message reception in a sensor unit.

The available counters are listed in tables 1 to 5.

#### 3.7.4 HET-EPT Analog Frontend Readout

A packet from the frontend board will contain at least the housekeeping ADC readings in unpacket format. The single channel trigger counters may be

usefull for high rate triggers. The frontend packet with items  $\max_{15}=0 \times 0110$  will provide the parameters at the offsets given in Table 8.

The ICU may define parameters with fixed semantics for the housekeeping ADC readings. These readings are prefixed with a 4-bit channel number which may need to be masked out when extracting the parameters. That's why the length is givel as 12 bits.

The single channel counters are 16 bits unsigned floating point. These may be extracted into general trigger parameters as required.

Table 8: Frontend parameters

| Name          | offset | length | description                    |

|---------------|--------|--------|--------------------------------|

| sc 00         | 2      | 16     | L1 trigger counter channel 0.  |

| sc01          | 4      | 16     | L1 trigger counter channel 1.  |

|               |        |        |                                |

| sc 29         | 60     | 16     | L1 trigger counter channel 29. |

| нк $400$      | 62     | 12     | HET preamp temperature         |

| ${ m HK}~500$ | 64     | 12     | EPT preamp temperature         |

| ${ m HK}~401$ | 66     | 12     | HET VREF, $+2.5\mathrm{V}$     |

| нк $501$      | 68     | 12     | EPT sensor temperature         |

| ${ m HK}~402$ | 70     | 12     | HET sensor temperature 1       |

| ${ m HK}502$  | 72     | 12     | EPT VFET/2, $+5 \mathrm{V}$    |

| ${ m HK}403$  | 74     | 12     | HET VFET/2, $+5 \mathrm{V}$    |

| нк $503$      | 76     | 12     | EPT $VANA/2$ , $+6V$           |

| ${ m HK}~404$ | 78     | 12     | HET sensor temperature 2       |

| нк $504$      | 80     | 12     | EPT VREF, $+2.5\mathrm{V}$     |

| нк $405$      | 82     | 12     | Shaper $VCC/2$ , $+5V$         |

| нк $505$      | 84     | 12     | Bias Current                   |

| нк $406$      | 86     | 12     | Power board temperature        |

| нк $506$      | 88     | 12     | Bias Voltage                   |

| нк $407$      | 90     | 12     | Analog board temperature       |

| нк $507$      | 92     | 12     | Digital board temperature      |

# 4 Data Acquisition

Various bits from the master control registers control the data acquisition process:

$enables_8[0]$ : event reception enable,

enables<sub>8</sub>[1]: L3 trigger enable,

enables<sub>8</sub>[2]: PHA storage enable,

enables<sub>8</sub>[4]: timestamp clock enable.

enables<sub>8</sub>[5]: analog frontend enable,

$confs_{16}[0]$ : high speed calibration mode enable,

confs<sub>16</sub>[1]: sample mode enable,

confs<sub>16</sub>[2]: L2 streaming mode enable,

### 4.1 Pulse Height Data Packets

When the L2 trigger in the analog board FPGA identifies a valid particle event, a data packet is sent to the digital board. There are eight L2 triggers, and each has an associated channel mask identifying the signal channels that are important to analyze the particle hit. Data is sent for all channels that are selected by any valid L2 trigger. The data packet starts with the channel mask.

Table 9: Event Pulse Height Packet Format

|   | 1 1 1 1 1 1 | Ox BEEF         | A128                                                  |                |

|---|-------------|-----------------|-------------------------------------------------------|----------------|

| R |             | channe          | elmask30                                              |                |

|   | trig8       | prescale8       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                |

|   |             | A <sub>18</sub> | BB <sub>10</sub>                                      | T <sub>4</sub> |

- - -

The MSB of the channel mask word identifies random triggers that are activated by strobes<sub>64</sub>[14]. Those event packets will contain data for all 30 channels.

The header further contains three fields

trigs: bitmask of L2 triggers.

prescale<sub>8</sub>: number of event packets that where dropped because the FIFOs were full, since the last transmitted packet.

dtime<sub>16</sub>: time since the last trigger in  $\mu$ seconds.

For each selected channel a record of 32 bits will be sent, containing three data fields

$A_{18}$ : pulse height, i.e., filter channel A.

BB<sub>10</sub>: pulse phase, i.e., filter channel B, ten bits selected by the leading bit in  $A_{18}$ .

$T_4$ : pulse age.

#### 4.1.1 Event Packet Reception

The digital board monitors the stream channel from the analog board for the sync header of event packets 0x BEEF A128 or sample packets 0x 5A61, and initiates the packet parser when it is idle, or when there where unrecognized data in the stream before the currently parsed packet. Event packet reception cannot be disabled at this stage.

The parser will capture the channel mask<sub>30</sub>, and expect as many channel records as requested. The data will be send to three destinations

- the L3 data set,

- the PHA data set, and

- in streaming mode to the telemetry FIFO.

The telemetry FIFO receives the packet unchanged, if streaming mode is enabled.

The L3 and PHA data sets are transferred simultaneously to the event buffer. Each data set contains 32 words with 32 bits each. The L3 data set will later be loaded into the L3 register file, the PHA data set will be saved in a PHA buffer when so instructed by the L3 processor.

The PHA data set receives the words from the event packet unchanged. The data for each signal channel will we written to a fixed position in the data set, i.e., unselected channels will be substituted with zeros in the data sets. PHA data is saved without EDAC protection into the external SRAM.

Table 10: L3 Data Set Format

| 0                                                     | $\begin{array}{c c} & \text{channel } \mathtt{mask}_{21:0} \\ \hline \end{array}$ |                   |  |                    |                        |

|-------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|--|--------------------|------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                                                                   | trig <sub>8</sub> |  | channel:           | $	exttt{nask}_{29:22}$ |

| A <sub>18</sub>                                       | (sign extended)                                                                   |                   |  | $0_{1}0_{1}0_{1}1$ | T <sub>4</sub>         |

- - -

The word size of the L3 trigger processor is only 29 bits because of EDAC overhead. Some reformatting is necessary to make sure all relevant data fits into the registers.

The L3 trigger will not receive the BB<sub>10</sub> fields of the channel records, nor the prescale<sub>8</sub> field of the headers. The dtime<sub>16</sub> field is truncated to 13 bits with overflow check.

L3 data set word 0 receives the part of the channel mask corresponding to HET channels. Word 1 receives the channel mask bits for EPT channels, and further header data. The remaining data set words are each associated with a fixed signal channel. For unselected channels all zeros are written. Available channel data are formatted such that the whole register value can be used as the pulse height, the data in the LSB contributing insignificant noise.

#### 4.1.2 L3 Event Class

The L3 trigger processor has four entry points, i.e., there can be four different programs called for different event classes. The event class is established by the packet reception unit from the L2 trigs bits.

The mapping from trig<sub>8</sub> to event class is provided by the trigger class<sub>16</sub> register, which can be set with

Command message:

| 1 | ı | 1 1 | 0x0    | 001               | 1 | ı | ı | ı |

|---|---|-----|--------|-------------------|---|---|---|---|

|   | ı | tri | ggercl | ass <sub>16</sub> | 1 | ı | ı |   |

The event class is a 2-bit number. The MSB of the event class is set, when any of the L2 trig<sub>8</sub> bits is active that is also set in the upper half of trigger class<sub>16</sub>[15:8]. The lower bit of the event class is set when any of the L2 triggers selected by the lower half trigger class<sub>16</sub>[7:0]] is set.

The proposed value for the trigger class<sub>16</sub> register is

|  | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |  |

|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

with a proposed configuration of L2 triggers

$trig_{8}[0]$ : EPT ion forward,

trig<sub>8</sub>[1]: EPT electrons backward,

trig<sub>8</sub>[2]: EPT ion backward,

trig<sub>8</sub>[3]: EPT electrons forward,

trig<sub>8</sub>[4]: HET forward stopping,

trig<sub>8</sub>[5]: HET forward penetrating,

trig<sub>8</sub>[6]: HET backward stopping,

trig<sub>8</sub>[7]: HET backward penetrating,

With this L2 trigger menu, the L3 trigger classes are:

- 0: EPT trigger, no HET triggers present.

- 1: HET forward stopping, no other HET triggers.

- 2: HET backward stopping, no other HET triggers.

- 3: Het penetrating.

EPT triggers are presumably more frequent than HET triggers. The class 0 program does not need to bother with HET. The HET programs need to check for possible EPT triggers as well. HET stopping trigger classes do not need to look for signals in the downstream detectors. HET penetrating needs to do the most work. The downstream hits may be crosstalk or it may be a real penetrating particle.

#### 4.1.3 Trigger and Prescale Counters

The data reception unit counts the occurrences of set bits in prescale<sub>8</sub> and trig<sub>8</sub> for all received event packets. The counters are located at address 0 to 7 (prescale<sub>8</sub>) and 8 to 15 trig<sub>8</sub> of the counter memory.

The counts of the prescale<sub>8</sub> bits can be weighed by bit significance and added together give the total number of events lost in the analog board.

#### 4.2 Event Buffer

L3 and PHA data sets are written into the event buffer memory, which is 128 word of 64 bits, excluding EDAC overhead. The words contain the L3 and PHA parts, 32 words for one data set. Four event data sets fit into the buffer memory.

Incoming event data is always written into the next available data set space. When the set is complete,

- if enables<sub>8</sub>[0] is not set, the data set will be discarded and ignored.

- Else, when the event buffer is full, the data set will be discarded, and counted as lost.

- Else, the data set is queued for processing by the L3 processor, i.e., the data set write pointer advances to the next slot.

#### 4.2.1 Feeding the L3 trigger processor

The L3 trigger processor operates on a register file with 256 registers. The L3 event data sets are loaded into the last 32 registers before the trigger is

executed.

When events are queued in the buffer, and the L3 trigger processor is idle, and the PHA storage unit is idle, the L3 processor is loaded and started. The data set memory space is then released from L3 but still locked for PHA storage. But all previous data sets are released from PHA at this point and become available for new incoming data.

The event buffer keeps track of the event class that was assigned to each data set. The L3 trigger is started at the instruction address with the event class as the two MSB and zeros in the LSB, i.e., at addresses  $0 \times 000$ ,  $0 \times 100$ ,  $0 \times 200$ , or  $0 \times 300$ .

#### 4.2.2 PHA storage

The L3 trigger processor may decide to save the PHA data sets into a PHA buffer in external memory. 16 buffers with 256 memory words of space are available, 32 bits each, 1kByte per buffer 16 kBytes total. L3 decides into which buffer the data shall go.

The idea is that rare events are saved in separate buffers, so they are not lost. The frequent events will fill their buffers fast and all further events will be dropped.

The PHA storage is not protected with EDAC redundancy. The data is not considered essential for science analysis. EDAC protected memory words leave only 26 bits, which is not a good match for the storage of PHA data. The location of the PHA buffers in the external memory is configured via phabase<sub>18:12</sub>.

The PHA storage unit keeps two counters for each PHA buffer. nevents<sub>24</sub> is the number of events that where supposed to be stored in the buffer, and nwords<sub>8</sub> is the pointer to the last word in the buffer that was written. These two counters are written into the first words of the PHA buffer for each event, i.e., nevents<sub>24</sub> continues to count when the buffer is full.

| nevents <sub>24</sub> | nwords8 |

|-----------------------|---------|

|                       |         |

The PHA data set is appended to the buffer data, until it is full. The end of a full buffer will likely contain an incomplete event data set. Only the event header and valid channel data are saved. The headers allow to reconstruct the storage size of each event.

The MSB of  $phabase_{18:12}$  is toggled with  $strobes_{64}[11]$ . That effectively saves the set of filled PHA buffers for telemetry readout, and make a new set available for data acquisition. The new set needs to be cleared with  $strobes_{64}[8]$ , which resets all internal copies of  $nevents_{24}$  and  $nwords_8$  to zero, and writes zeros into the first word of each PHA buffer.

## 4.2.3 Test Data Injection

Test data can be injected into the PHA buffer via command messages to address  $0x\,0003$ . A message with size tag zero resets the input register pointer, i.e., the next data will go into slot 0 of the event data set.

| Command message: |         |  |  |  |  |  |  |  |

|------------------|---------|--|--|--|--|--|--|--|

| 0                | 0x 0003 |  |  |  |  |  |  |  |

Messages with size 64-bits write into the next word of the event buffer, with the PHA data in the upper half of the data word and the L3 data in the lower half.

| Command | message: |

|---------|----------|

|         |          |

| 3 | 0x 0003                                                                                                |             |       |     |     |       |

|---|--------------------------------------------------------------------------------------------------------|-------------|-------|-----|-----|-------|

|   | <pha d.<="" td=""><td>ATA SET &gt; 1</td><td>1 1 1</td><td>1 1</td><td></td><td></td></pha>            | ATA SET > 1 | 1 1 1 | 1 1 |     |       |

|   | <l3 da<="" td=""><td>TA <math>SET</math></td><td>1 1 1</td><td>1 1</td><td>1 1</td><td>1 1 1</td></l3> | TA $SET$    | 1 1 1 | 1 1 | 1 1 | 1 1 1 |

The data set is submitted by a message with data size 16-bits. The two LSB encode the event class.

| Con | Command message: |   |   |   |   |   |  |   |   |   |   |    |

|-----|------------------|---|---|---|---|---|--|---|---|---|---|----|

| 1   | 0x 0003          |   |   |   |   |   |  |   |   |   |   |    |

|     |                  | ı | ı | i | ı | ı |  | ı | 1 | 1 | ı | ec |

The analog frontend should be disabled when the injection is in use, else the data may collide with real triggers.

#### 4.2.4 Event Data Formats

$\dots$ TODO

# 4.3 L3 trigger

The L3 trigger is a programmable processor with separate program and register memory.